电路设计

由于 A111 的灵敏度很高,因此需仔细设计电路布局。一般情况下,建议使用接地层结构,所有接地引脚(1、3、4、6、10、11 和 9)均连接到此层。输入和输出线应尽量分开,在大多数情况下都需要屏蔽。应特别注意探测器的接地连接,避免由于反馈而产生多次脉冲和振荡。电源电压内部去耦,可防止 A111 对高达 100 mV 振幅的电源线瞬变作出响应。虽然这通常已足够,但在某些应用程序中,外部旁路(通常为 10 nF )可能会很有用。PC21 可用作合适布局设计的一个例子。

电源

虽然给出了 +5 V 工作电压规格,但 A111 的特性一般不受电源电压在 4 到 10V 区间内波动的影响。对特定应用至关重要的参数应在实际工作电压下进行检查。

输入

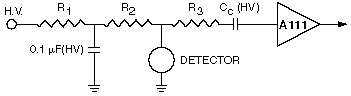

A111 有一个包括耦合电容器的内部输入保护网络,如下所示。但是,它无法对通过输入的高压放电提供充分的保护。

应牢记两个注意事项:

1. 探测器阳极通常应通过具有适当额定电压的电容与引脚 12 进行电容耦合,以便在工作条件下不会被击穿。在某些应用中,探测器阴极在负电位下工作,阳极可直接连接到引脚 12。

2.打开探测器偏压时,探测器的高电压上升速度应足够慢,以防止大型瞬态电流通过耦合电容进入输入。这一点通常由具有适当额定电压的组件的高压 RC 滤波网络提供保障。

一般而言,应避免任何电路部分出现高压放电。

例如:

通常 R1、R2 > 1 M

R3 可选附加保护用于限制输入电流,通常小于 1 k

A111 将对 8 x 10-15 库仑或更高的负脉冲作出响应。阈值可以通过在引脚 7 和 8 之间连接一个电阻来增加。规格参数下的图 1“阈值与电阻之间的关系”给出了近似值。

此设备针对负输入脉冲进行了优化,它将对大于负阈值约 2 倍的正输入脉冲作出响应。由于此处提供的规格适用于负输入,因此用户应测量任何正输入应用的所有相关工作特性。

通过使用小电容(通常为 1 或 2 pF)将测试电荷注入输入,可借助脉冲发生器对 A111 进行测试。该装置将在测试脉冲的下降沿触发,其过渡时间应小于 20 ns。此下降沿后面应为相对平坦的波形部分,以便它显示为阶跃函数。例如,方波是一个很好的测试波形。(当使用方波时,应注意装置在振幅超过 2 倍阈值时也会对上升沿作出响应。)另外,也可以使用“锯齿”波或下降时间较长(> 1 µs)的拖尾脉冲。

典型测试电路

上升时间:< 20 ns(下降沿)

振幅:500 mV/皮库仑;标称阈值时为 4 mV。

到输入的电荷根据 Q = Ct·V 进行转移,其中 Q = 总电荷,Ct = 测试电容器的值,V = 电压阶跃幅度。请勿直接或经由大电容器(> 100 pF)将测试脉冲发生器连接到输入端,因为这样会在输入晶体管中产生大电流并导致不可逆的损坏。

输出

A111 的输出电路是一个具有 6 千欧集电极接地负载的 PNP 晶体管:

此电路直接驱动 CMOS 输入,具有宽电压摆动,因此具有出色的抗噪性。高值(6 千欧)负载电阻可在关键应用中最大程度地减少内部接地电流和功耗。在负载电容较大且高计数率性能非常重要的应用中,在引脚 5 到接地之间添加一个外部电阻 Rx 将缩短输出脉冲的下降时间。负载电容 10 至 50 pF 的典型电阻值为 2 千欧。在牺牲脉冲振幅的情况下,可以驱动低阻抗电路,例如端接同轴电缆。例如,端接的 50 欧姆电缆可以以 1.4 V(Vs = 5 V)的脉冲振幅驱动。

要将 A111 直接与 TTL 连接,必须选择一个 Rx 值来吸收 TTL 设备所需的低电平输入电流。例如,对于要求在 0.4 V 时 Iin = 0.4 mA 的低功耗设备,与 6 千欧并联的最大 Rx 为 1 千欧。对于需要吸收 2 mA 以上电流的器件,建议在 A111 和输入之间采用反相 NPN 晶体管连接。

A111 线路驱动器

其他阈值调整

A)增加 A111 的阈值:

如图所示,通过通过短接引脚7和8的 RC 反馈电路可将 A111 的阈值增加到 10 倍以上。

撇开装置之间的差异,鉴别水平如下:

-

- 引脚 7 和 8 短路将导致标称阈值增加 10 倍:(5 x 104 个电子)x 10 = 5 x 105 个电子。

- 引脚 7 和 8 短路,外加反馈:

R = 50 k C = 2.2 pF : 17xR = 20 k C = 3.3 pF : 23xR = 5 k C = 4.7 pF : 40xR = 2 k C = 6.8 pF : 88x

可通过调整 R 值获得中间值

B)降低 A111 的阈值:

通过在引脚 8 和接地之间添加一个电阻,可以将 A111 的阈值降低到标称 5 x 104 个电子以下。一个 300 欧姆电阻将使灵敏度增加一倍左右,从而产生 2.5 x 104 个电子的阈值。